# **IDEC** Chip Pesign Contest An Electrical Stimulation IC with Chopped Pulse based Active Charge Balancing

Jin-Young Son and Hyouk-Kyu Cha

Dept. of Electrical and Information Engineering, Seoul National University of Science and Technology

jyson@seoultech.ac.kr, hkcha@seoultech.ac.kr

## MOTIVATION

• Neural stimulators can be used for the treatment of neurological disorders such as epilepsy, Parkinson's disease, and Alzheimer's, as well as to help restore body impairments such as in retinal and cochlear implants [1, 2]. In this work, an implantable HV compliance current

mode neural stimulator integrated circuit (IC) using novel active charge balancing technique is proposed. The proposed charge balancing technique using chopped pulse waveform can minimize the amount of residual potential at the electrode. The stimulator IC designed using 0.18- $\mu$ m standard CMOS process achieves 12.3 V of voltage compliance without reliability issue and can limit the electrode residual potential to a negligible level. All circuit functions are integrated on-chip without external components, and the fabricated chip consumes only 0.095 mm<sup>2</sup> of active area.

## - CIRCUIT DESIGN

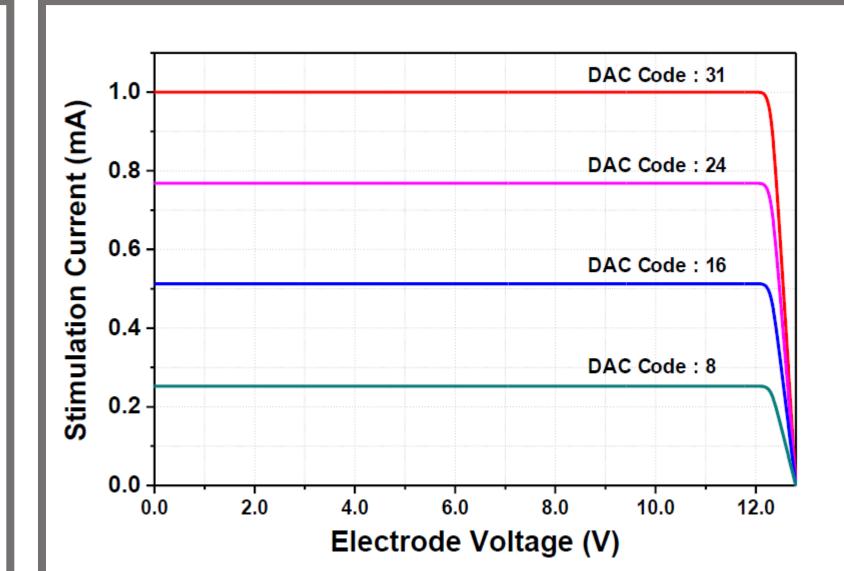

#### Fig 4. Measured voltage compliance

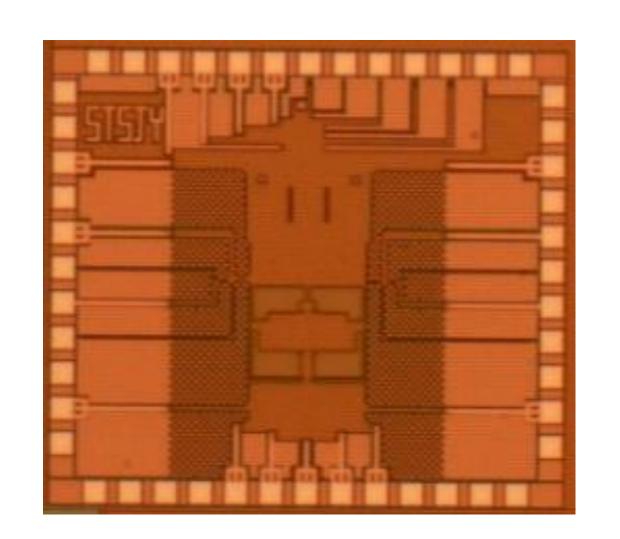

#### Fig 5. Chip Micrograph

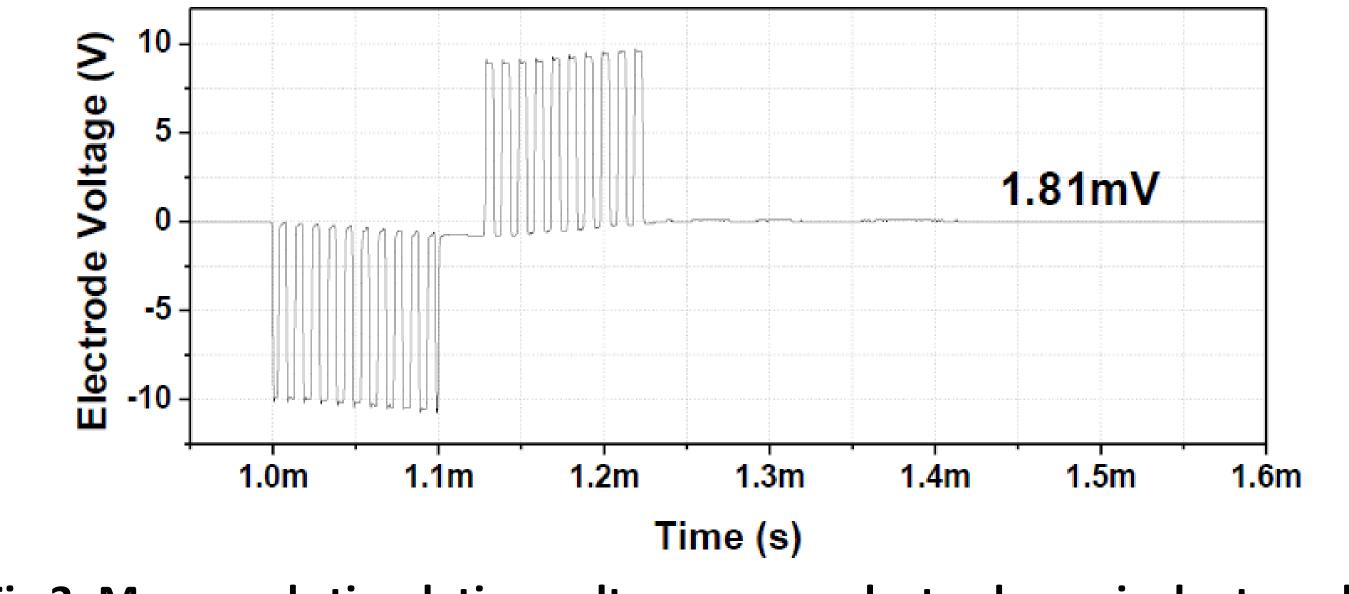

• Figure 3 shows the measured stimulation voltage across electrode equivalent model with enabled active charge balancing and electrode shorting. Figure 4 shows measured voltage compliance for different DAC codes. Figure 5 shows the chip micrograph.

## • PERFORMANCE SUMMARY

| Parameter                                          | This work                                                      | [2]                                                   | [3]                   | [4]                                          |

|----------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------|-----------------------|----------------------------------------------|

| Voltage<br>Compliance                              | 12.3 V                                                         | 12.3 V                                                | < 20 V                | < 20 V                                       |

| Maximum<br>Stimulation<br>Current                  | 1 mA                                                           | 1 mA                                                  | 1.2 mA                | 10 mA                                        |

| Current<br>DAC<br>Resolution                       | 5-bit                                                          | 5-bit                                                 | 10-bit                | 6-bit                                        |

| Waveform                                           | Symmetric/<br>Asymmetric<br>Chopped<br>Biphasic                | Biphasic                                              | Biphasic              | Symmetric<br>Chopped<br>Biphasic             |

| Charge<br>Balancing                                | Chopped<br>Pulse based<br>& Automatic<br>Electrode<br>Shorting | Anodic Pulse<br>Modulation<br>& Electrode<br>Shorting | Pulse<br>Insertion    | Pulse<br>Insertion                           |

| Residual<br>potential<br>after charge<br>balancing | < 3 mV                                                         | < 22 mV                                               | < 30 mV               | -                                            |

| Power<br>Efficiency                                | 50%<br>@ 20%<br>stimulation<br>duty ratio                      | 44.8%<br>@ 20%<br>stimulation<br>duty ratio           | -                     | 36-51%<br>@ 20%<br>stimulation<br>duty ratio |

| Process                                            | 0.18-μm<br>Standard<br>CMOS                                    | 0.18-μm<br>Standard<br>CMOS                           | 0.18-μm 24V<br>LDMOS  | 0.18-μm HV<br>CMOS                           |

| Area                                               | 0.095 mm²                                                      | 0.11 mm <sup>2</sup>                                  | 0.105 mm <sup>2</sup> | 3.36 mm <sup>2</sup><br>(include<br>PAD)     |

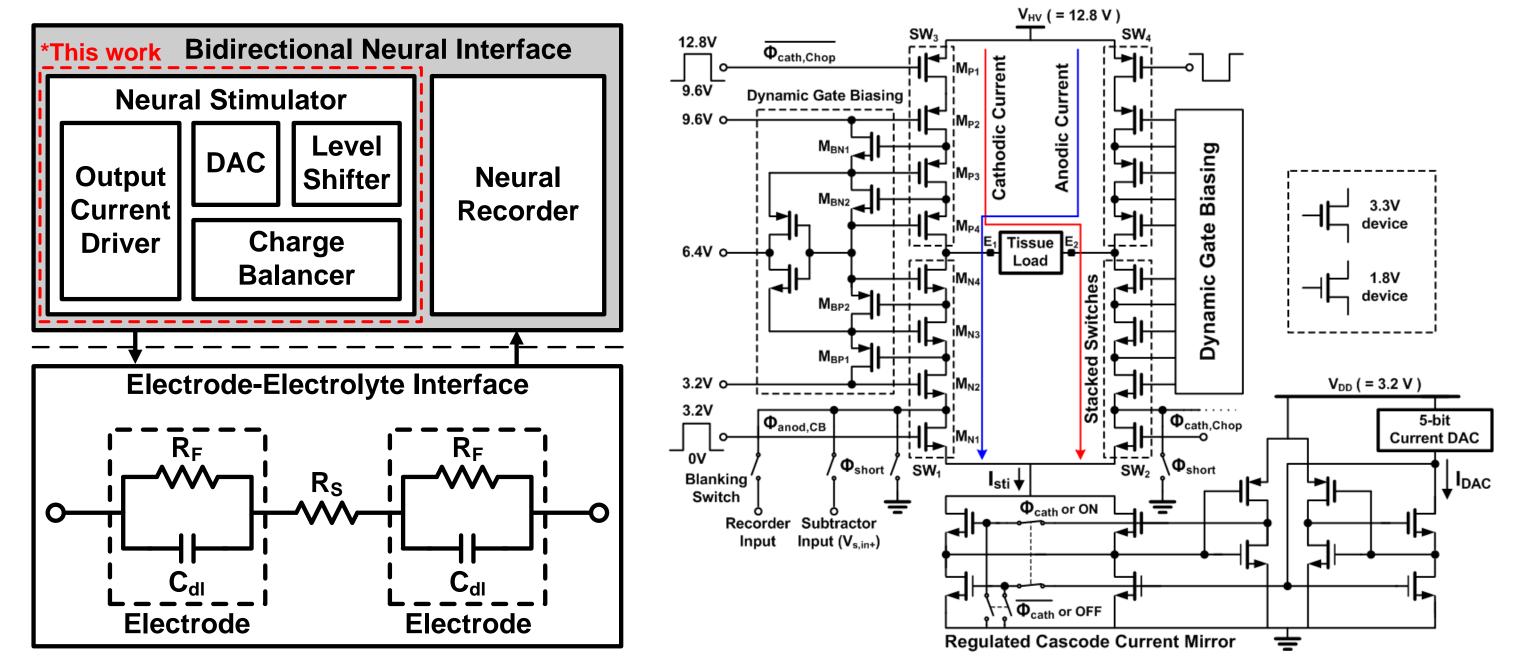

#### Fig 1. Block Diagram of stimulator IC

#### Fig 2. Proposed output driver

- Figure 1 shows the block diagram of the proposed stimulator system architecture and the equivalent electrode model used in the design. The stimulator system is comprised of a current-steering digital-to-analog converter (DAC), level-shifter, output current driver, and charge balancer circuits.

- Figure 2 shows the schematic of the regulated cascode current mirror and the output current driver used in the proposed stimulator IC. In the regulated cascode current mirror circuit, 1.8-V devices and 3.3-V devices are appropriately used for high output resistance and low voltage headroom. High supply voltage greater than 10 V is required to deliver up to 1 mA of current to 10 k $\Omega$  of tissue load. Each switch is implemented by four stacked 3.3-V transistor devices. The stacked devices are biased through the dynamic gate biasing circuit to keep the voltage across each terminal within 3.2 V to prevent breakdown due to the high supply voltage

## SIMULATION/EXPERIMENTAL RESULTS

## - CONCLUSION

• A current-mode neural stimulator IC with novel active charge balancing technique using chopped pulse waveform and a simple charge balancer circuit is proposed and designed using 0.18-µm standard CMOS process.

# ACKNOWLEDGEMENTS

This research was partly supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science and ICT (MSIT), (NRF-2018R1C1B6003088) and Institute for Information & Communications Technology Promotion (IITP) grant funded by MSIT (No. 2017-0-00659). The chip fabrication and EDA

Fig 3. Measured stimulation voltage across electrode equivalent model load

tool were supported by the IC Design Education Center (IDEC).

### REFERENCE

[1] B. K. Thurgood et al., "Wireless integrated circuit for 100-channel neural stimulation," in 2008 IEEE Biomed. Circuits and Syst. Conf., Nov 2008, pp.129–132.

[2] J.-Y. Son and H.-K. Cha, "An implantable neural stimulator IC with anodic current pulse modulation based active charge balancing," IEEE Access, vol. 8, pp. 136449-136458, Jul. 2020

[3] L. Yao, P. Li and M. Je, "A pulse-width-adaptive active charge balancing circuit with pulse-insertion based residual charge compensation and quantization for electrical stimulation applications," 2015 IEEE Asian Solid-State Circuits Conference (A-SSCC), Xiamen, 2015, pp. 1-4

[4] M. N. van Dongen and W. A. Serdijn, "A power-efficient multichannel neural stimulator using high-frequency pulsed excitation from an unfiltered dynamic supply," IEEE Trans. Biomed. Circuits Syst., vol. 10, no. 1, pp. 61–71, Feb. 2016